- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC16C765T-I/L (Microchip Technology)IC MCU OTP 8KX14 USB 44PLCC

PIC16C745/765

DS41124C-page 26

Preliminary

2000 Microchip Technology Inc.

4.2.2.5

PIR1 REGISTER

This register contains the individual flag bits for the

peripheral interrupts.

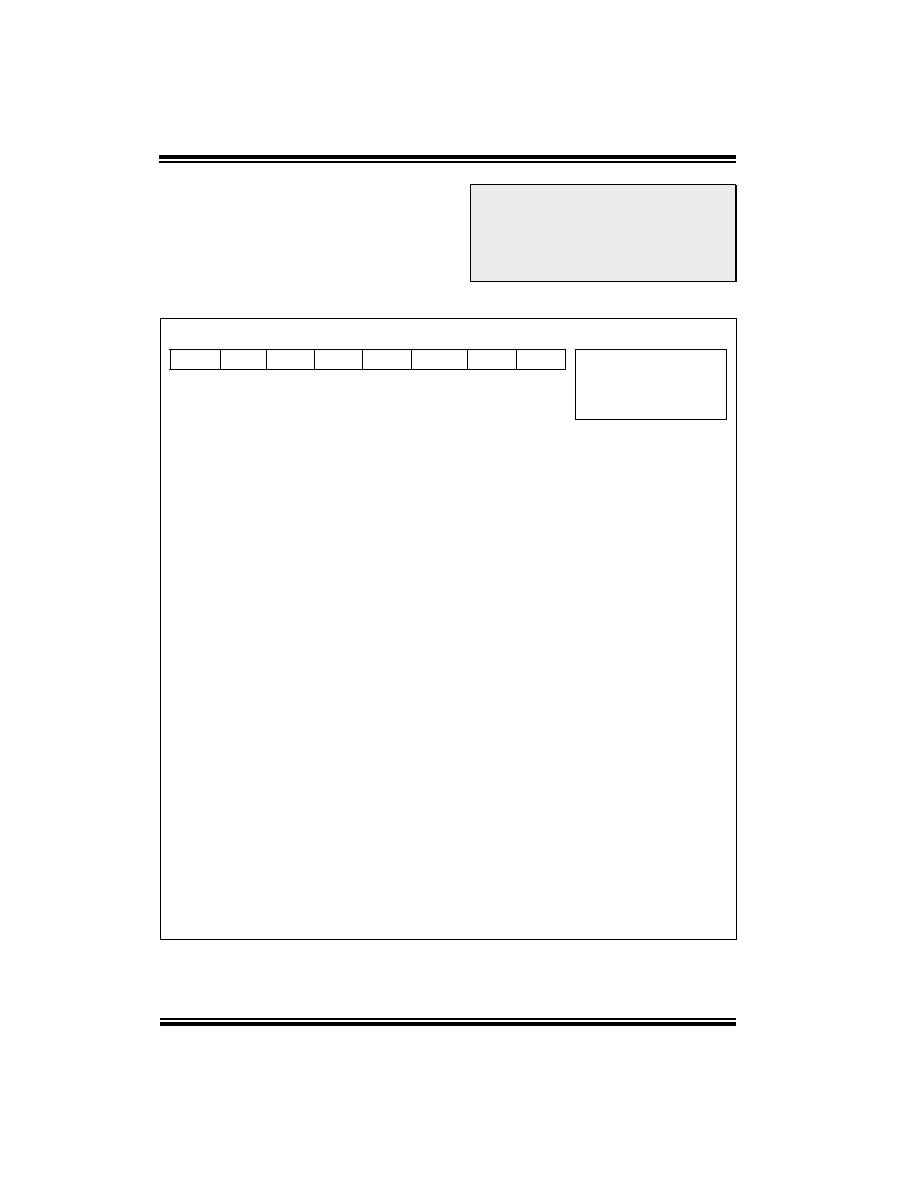

REGISTER 4-5:

PERIPHERAL INTERRUPT REGISTER1 (PIR1: 0Ch)

Note:

Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User soft-

ware should ensure the appropriate inter-

rupt flag bits are clear prior to enabling an

interrupt.

R/W-0

R-0

R/W-0

PSPIF(1)

ADIF

RCIF

TXIF

USBIF

CCP1IF

TMR2IF TMR1IF

R = Readable bit

W = Writable bit

U = Unimplemented bit,

read as ‘0’

-n = Value at POR reset

bit7

bit0

bit 7:

PSPIF(1): Parallel Slave Port Read/Write Interrupt Flag bit

1

= A read or a write operation has taken place (must be cleared in software)

0

= No read or write has occurred

bit 6:

ADIF: A/D Converter Interrupt Flag bit

1

= An A/D conversion completed (must be cleared in software)

0

= The A/D conversion is not complete

bit 5:

RCIF: USART Receive Interrupt Flag bit

1

= The USART receive buffer is full (clear by reading RCREG)

0

= The USART receive buffer is empty

bit 4:

TXIF: USART Transmit Interrupt Flag bit

1

= The USART transmit buffer is empty (clear by writing to TXREG)

0

= The USART transmit buffer is full

bit 3:

USBIF: Universal Serial Bus (USB) Interrupt Flag

1

= A USB interrupt condition has occurred. The specific cause can be found by examining the contents

of the UIR and UIE registers.

0

= No USB interrupt conditions that are enabled have occurred.

bit 2:

CCP1IF: CCP1 Interrupt Flag bit

Capture Mode

1

= A TMR1 register capture occurred (must be cleared in software)

0

= No TMR1 register capture occurred

Compare Mode

1

= A TMR1 register compare match occurred (must be cleared in software)

0

= No TMR1 register compare match occurred

PWM Mode

Unused in this mode

bit 1:

TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1

= TMR2 to PR2 match occurred (must be cleared in software)

0

= No TMR2 to PR2 match occurred

bit 0:

TMR1IF: TMR1 Overflow Interrupt Flag bit

1

= TMR1 register overflowed (must be cleared in software)

0

= TMR1 register did not overflow

Note 1: Parallel slave ports not implemented on the PIC16C745; always maintain this bit clear.

745cov.book Page 26 Wednesday, August 2, 2000 8:24 AM

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C442T-E/L

IC MCU OTP 8KX16 A/D 44PLCC

PIC16C621A-40/SS

IC MCU OTP 1KX14 COMP 20SSOP

PIC16C622A-40/SS

IC MCU OTP 2KX14 COMP 20SSOP

PIC16CE623-30/SO

IC MCU OTP 512X14 EE COMP 18SOIC

PIC16CE624-30/SO

IC MCU OTP 1KX14 EE COMP 18SOIC

PIC16CE624-30/SS

IC MCU OTP 1KX14 EE COMP 20SSOP

PIC16CE623-30/SS

IC MCU OTP 512X14 EE COMP 20SSOP

PIC16CE624-30/P

IC MCU OTP 1KX14 EE COMP 18DIP

相关代理商/技术参数

PIC16C765T-I/PT

功能描述:8位微控制器 -MCU 14KB 256 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-04/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-04E/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-04I/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-10/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-10E/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-10I/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C76T-20/SO

功能描述:8位微控制器 -MCU 14KB 368 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT